Apple启动全新自研芯片研发前,会先开展6至12个月的前期技术预研与市场预判,由芯片研发、产品规划、硬件工程、系统软件多团队联合召开跨部门研讨会,结合未来两代终端产品迭代需求、半导体制程工艺节奏、供应链产能、竞品技术路线及市场消费趋势,完成全方位前期调研。

预研阶段会同步测试前沿电路设计、新型核心架构、低功耗晶体管等核心技术,验证方案可行性,同时与台积电等代工厂敲定制程进度、产能预留与成本预算,全面评估技术风险、研发投入与周期,明确芯片晶体管规模、CPU/GPU/NPU核心性能指标、ISP升级要点、接口兼容方案,以及芯片物理尺寸、封装形式、散热与功耗适配标准,最终形成完整立项报告,通过内部高层技术评审后,成立专项研发项目组,划分架构设计、前端开发、物理设计、验证测试、系统适配、供应链对接等细分团队,明确各环节节点与分工,正式开启芯片研发。

进入顶层架构设计阶段,项目组基于预研成果开展精细化微架构拆分设计,CPU团队自主研发高性能大核与高能效小核架构,优化指令集分支预测、执行单元、缓存层级、乱序执行效率与多核调度逻辑,针对移动、桌面不同使用场景,精准调校核心主频、功耗曲线与唤醒速度;GPU团队规划渲染核心、纹理填充与计算单元阵列,优化光线追踪、显存带宽利用,兼顾多场景图形算力需求;NPU团队搭建神经网络运算阵列,设计AI推理加速引擎,提升本地AI模型与多模态数据处理效率,适配系统AI功能迭代。

团队还会自主设计ISP图像处理器、视频编解码、安全加密、外设接口、内存与电源管理等全功能IP核,规划芯片片上互联总线架构,确定各模块数据传输、带宽分配与延迟控制方案,统筹整体功耗、电压调节与热分布管控。

每个模块架构都经过数十次仿真推演与方案迭代,反复平衡性能、功耗与芯片面积,最终形成完整顶层架构方案,交付前端团队进行逻辑实现。

前端逻辑开发环节,工程师采用Verilog、SystemVerilog硬件描述语言,将架构方案转化为数字电路逻辑代码,逐一定义晶体管开关、数据运算、指令执行与信号传输逻辑,从基础逻辑门、触发器、存储单元,逐步搭建起全功能模块逻辑体系。

代码编写严格遵循Apple内部设计规范,兼顾可综合性、可验证性,同时针对低功耗、高稳定性、抗电磁干扰做专项优化,M系列、A系列芯片逻辑代码量达数百亿行,覆盖数十亿电路节点。

代码完成后进入多层级前端功能验证,先开展单元级验证,测试单个最小模块逻辑正确性;再进行模块级验证,检测相邻模块数据交互与协同运行;最后通过超算服务器搭建虚拟环境,开展系统级全芯片仿真,模拟日常待机、重度运算、高低温环境、长时间满负载等数百种实际工况,借助形式化验证、随机测试、故障注入等技术,全面排查逻辑漏洞、时序冲突、数据异常、功耗超标等问题。

发现缺陷即刻回溯修改代码,重新完成全流程仿真,直至前端验证覆盖率达100%,确保芯片底层逻辑无缺陷,这一阶段占据整体研发近半数时间。

前端验证通过后,进入物理设计与版图实现阶段,物理设计团队将逻辑代码转化为符合半导体工艺的芯片物理版图,先完成逻辑综合,将代码转为标准单元电路库,再开展布局规划,按功能分区精准排布CPU、GPU、NPU等核心模块,合理预留电源、接地与信号走线空间,严格遵循制程设计规则,规避信号串扰、电流压降、局部发热等问题。

随后进行全局与详细布线,依托多层金属互联工艺,规划海量电路走线,优化线路长度与绕线方式,降低信号延迟与功耗损耗,对高频、供电线路做专项优化,保障信号与供电稳定;同时开展功耗与热仿真,预判芯片运行时的电流、电压与热量分布,通过调整布局、优化线路改善散热、减少漏电。

版图设计过程中,同步完成设计规则检查、原理图一致性校验,确保物理版图匹配逻辑设计、符合代工厂纳米级制造要求,最终生成高精度GDSII光刻版图文件,作为芯片制造的核心施工图纸。

版图定稿后,启动全方位后端物理验证,验证团队从时序、功耗、物理、工艺多维度开展严苛检测,先进行时序验证,分析信号传输延迟,确保全场景时序收敛,避免时序故障;再开展电压降、电迁移验证,保障芯片供电稳定,防止大负载下线路损坏;同时完成电磁兼容、热可靠性、工艺良率验证,排查制造缺陷、良率不足、长期可靠性差等问题,针对验证出的设计缺陷反复优化版图,直至所有指标达标,满足量产工艺要求。

所有设计验证完成后,Apple向台积电提交光刻版图,启动首次工程流片。

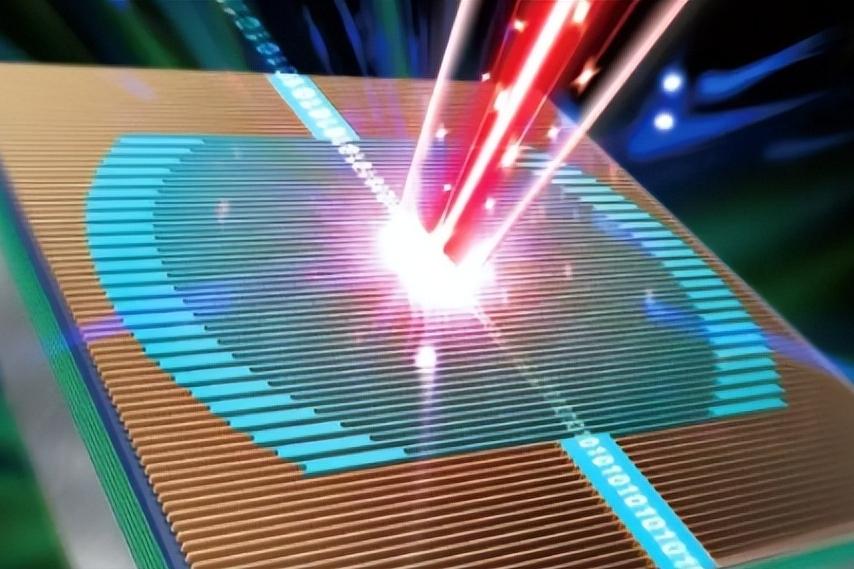

台积电采用对应高端制程,在高纯度硅晶圆上通过沉积、离子注入、EUV光刻、刻蚀等数十道精密工序,逐层复刻芯片电路,首批仅生产小批量工程样品,流片周期6至10周,成本高达数千万美元。

工程晶圆运回Apple实验室后,进入样片实测与迭代阶段,工程师切割晶圆取出裸片,完成初步封装后开展芯片级独立测试,检测主频、性能、功耗与功能完整性,再将芯片搭载至原型机,进行整机全场景实测,涵盖长时间满负载、高低温适配、待机续航、系统兼容、长期老化等数百项测试,精准记录各项性能隐患。

初代流片样品普遍存在性能、功耗、散热问题,研发团队依据测试数据回溯修改架构、代码与版图,进行2至4次重复流片与全面调校,直至芯片各项指标完全达标,最终冻结设计方案,不再做结构改动。

设计方案确定后,进入大规模量产阶段,Apple与台积电签订量产订单,锁定高端制程产能,代工厂按定稿版图与工艺批量生产晶圆,持续优化良率。

量产晶圆运送至封装测试厂后,经激光切割分为单颗裸片,再根据产品定位选择对应封装形式,完成基板贴合、引脚焊接、屏蔽与散热加固等工序。

封装完成后,通过专业设备对每颗芯片进行电性测试、功能全检、高低温老化与抗干扰测试,筛选出合格芯片,并按性能、功耗分级分选,适配不同终端产品。

合格芯片入库后,系统软件与硬件适配团队开展软硬件深度适配,针对芯片架构特性,优化iOS、macOS等系统底层内核,定制专属功耗管理、性能调度、AI加速与图形优化方案,实现软硬件无缝协同,最大化释放芯片能效,同时调校整机器温控、续航与功能兼容性。

完成全部适配测试后,芯片正式投入终端产品量产组装,搭载于iPhone、iPad、Mac等设备,经整机测试、质检与出厂校验后推向市场。从前期预研到最终上市,一颗Apple自研芯片研发周期长达18至24个月,研发投入超十亿美元,全程严苛的技术管控与品质打磨,让芯片在性能、能效与稳定性上始终保持行业顶尖水平。